US008671381B1

# (12) United States Patent Wang et al.

US 8,671,381 B1

(45) **Date of Patent:**

(10) **Patent No.:**

Mar. 11, 2014

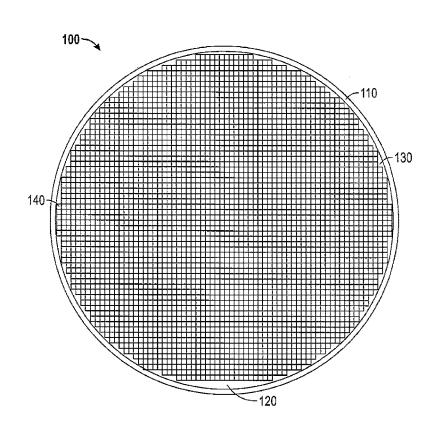

# (54) SYSTEM FOR OPTIMIZING NUMBER OF DIES PRODUCED ON A WAFER

(71) Applicants: **Peidong Wang**, Suzhou (CN); **Zhijun Chen**, Suzhou (CN); **Zhihong Cheng**,

Suzhou (CN); **Li Ying**, Suzhou (CN)

(72) Inventors: Peidong Wang, Suzhou (CN); Zhijun Chen, Suzhou (CN); Zhihong Cheng, Suzhou (CN); Li Ying, Suzhou (CN)

(73) Assignee: Freescale Semiconductor, Inc., Austin, TX (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

(21) Appl. No.: 13/723,207

(22) Filed: Dec. 21, 2012

(51) **Int. Cl. G06F 17/50** (2006.01)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 6,522,940<br>7,033,847<br>7,353,077<br>7,882,481<br>8,239,788 | B2<br>B2<br>B2<br>B2 | 8/2012           | Tai<br>Lin<br>Hempel<br>Lin                                                             |

|---------------------------------------------------------------|----------------------|------------------|-----------------------------------------------------------------------------------------|

| 8,386,981<br>2004/0128630<br>2009/0007028                     | B1 *<br>A1 *         | 2/2013<br>7/2004 | McGowan et al.       716/122         Ward et al.       716/2         Hempel       716/2 |

<sup>\*</sup> cited by examiner

${\it Primary Examiner} - {\rm Binh \ Tat}$

(74) Attorney, Agent, or Firm — Charles Bergere

### (57) ABSTRACT

A system for optimizing the number of dies that can be fabricated on a wafer uses a die number optimization (DNO) routine to determine a maximum number of dies for a target die area (TDA), and generate an initial result list of die shapes that have the maximum number of dies for the TDA. Optionally, a die size optimization (DSO) routine can be executed to determine a list of die shapes having a maximum die area corresponding to the maximum number of dies, a first list of optimized die shapes having a maximum area utilization (AU) for a decreased TDA, and/or a second list of optimized die shapes having a minimum AU for an increased TDA. A candidate list (CL) of the various die shapes can be generated, and entries from the CL automatically selected and/or displayed to indicate proposed wafer layouts.

# 24 Claims, 11 Drawing Sheets